芯片设计

RTL功耗设计解决方案

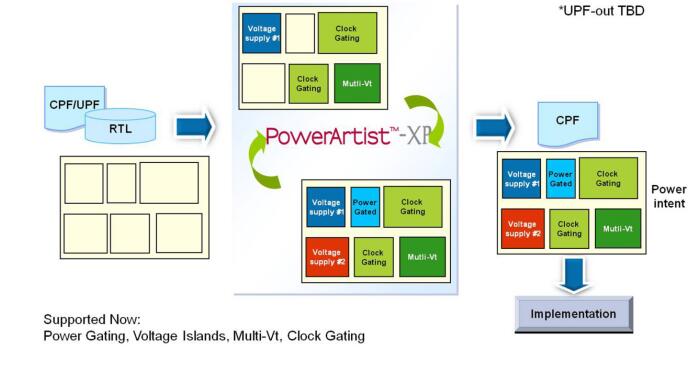

着集成电路业的发展,电子产品的电路密度迅速增加,工作频率也迅速提高,导致其功耗密度越来越大,单位面积上过高的功耗往往会降低电子产品的可靠性和使用寿命,对于各种便携式设备,高功耗更是致命的缺陷,附加散热设备不仅增加封装成本,而且降低电路集成度,如何减少电子产品的功耗已经逐渐成为IC行业研究的热点。ANSYS推出面向RTL功耗设计的综合性解决方案,执行物理感知 RTL 功耗预算、交互调试、分析驱动型降耗、功耗回归以及得到实时应用的功耗波形,又有助于实现一种可无缝衔接 RTL到物理设计的检查电源完整性的方法。其解决方案特点如下:

加快了数百万实例设计的迭代时间,并且有助于及早做出功耗相关的设计决定。

提供始终精确的 RTL 功耗值,并可识别降低功耗的机会。

自动识别时钟网络、数据路径以及存储器体系结构中的模块级、实例级的时序电路及组合电路的降耗机会,以最大程度的实现功耗目标。

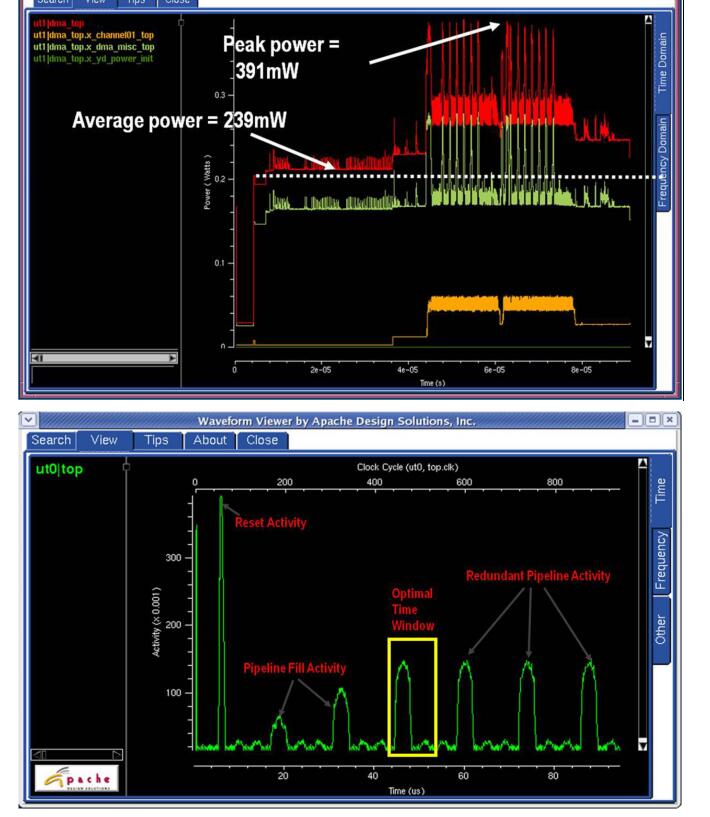

业界最快的功耗分析能力,比传统方法快好几个数量级,可以在数小时内分析包含几十毫秒的实时应用程序活动。

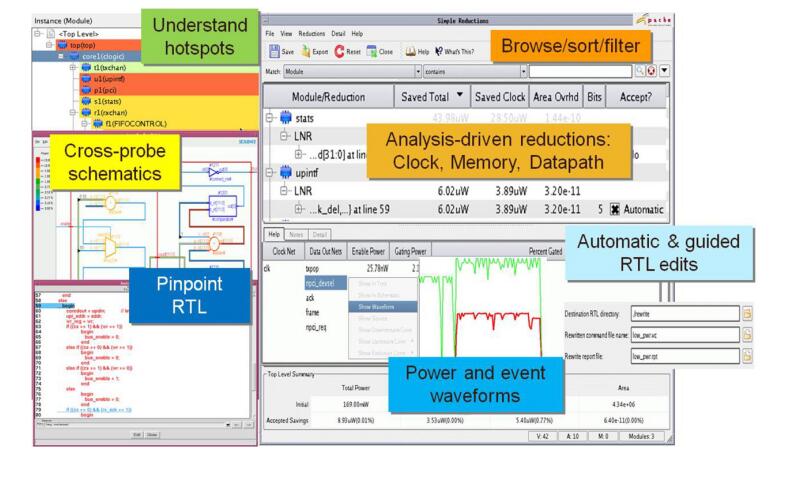

1. 图形工具辅助完成功耗优化

2. 功耗原型辅助完成假设分析,监测SoC级和后期功耗优化技术的影响

ANSYS软件,MENTOR软件,MSC软件,仿真培训及咨询----武汉恩硕科技有限公司 服务热线:400- 6600- 365

地址:湖北省武汉市武昌区和平大道三角路水岸国际一号楼2611